Hi, I got some question after read

Accessing Multiple Registers at Once | Verification Gentleman Blog article.

Basically the AHB has 2 phases transactions meaning that there are READ transaction that I send , I get the read data back in the next cycle. Could you let me know how you handle for this to resolve?

To get a delayed read data in a driver, I could add one clock sample @(posedge clk). this cause delay cycle for every read transaction. I think this is not the good way.

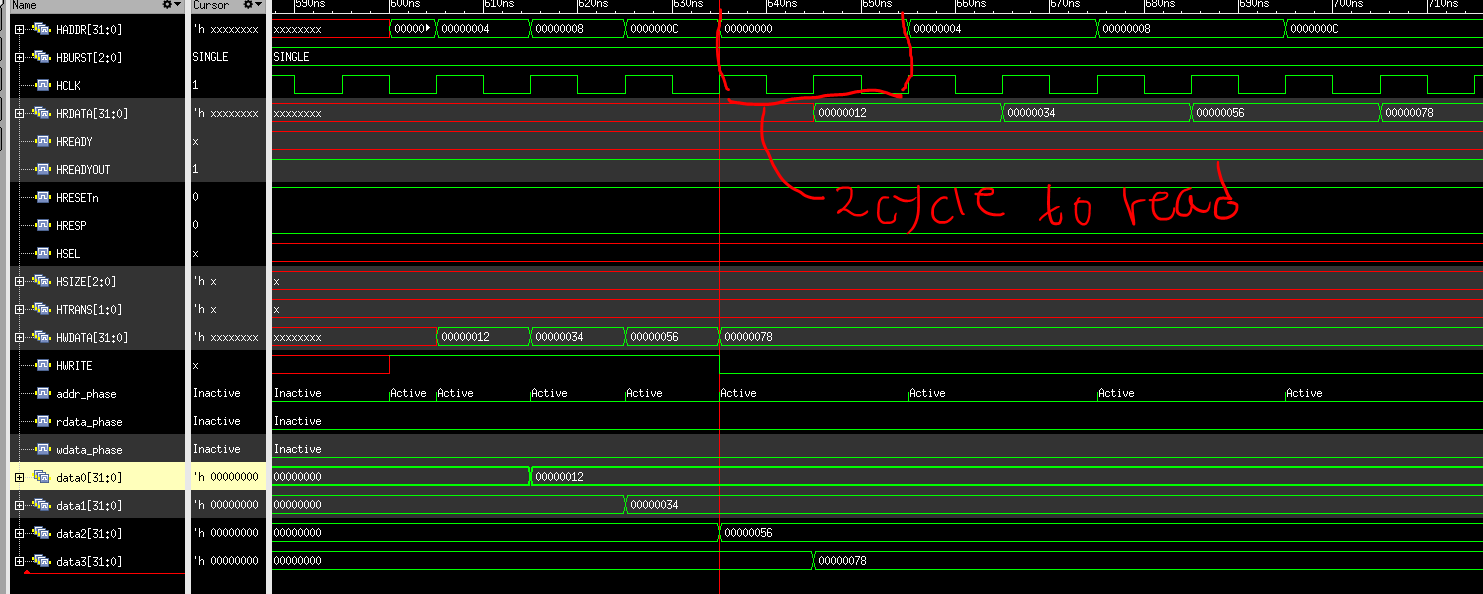

This is for read waveform wait with one cycle delay

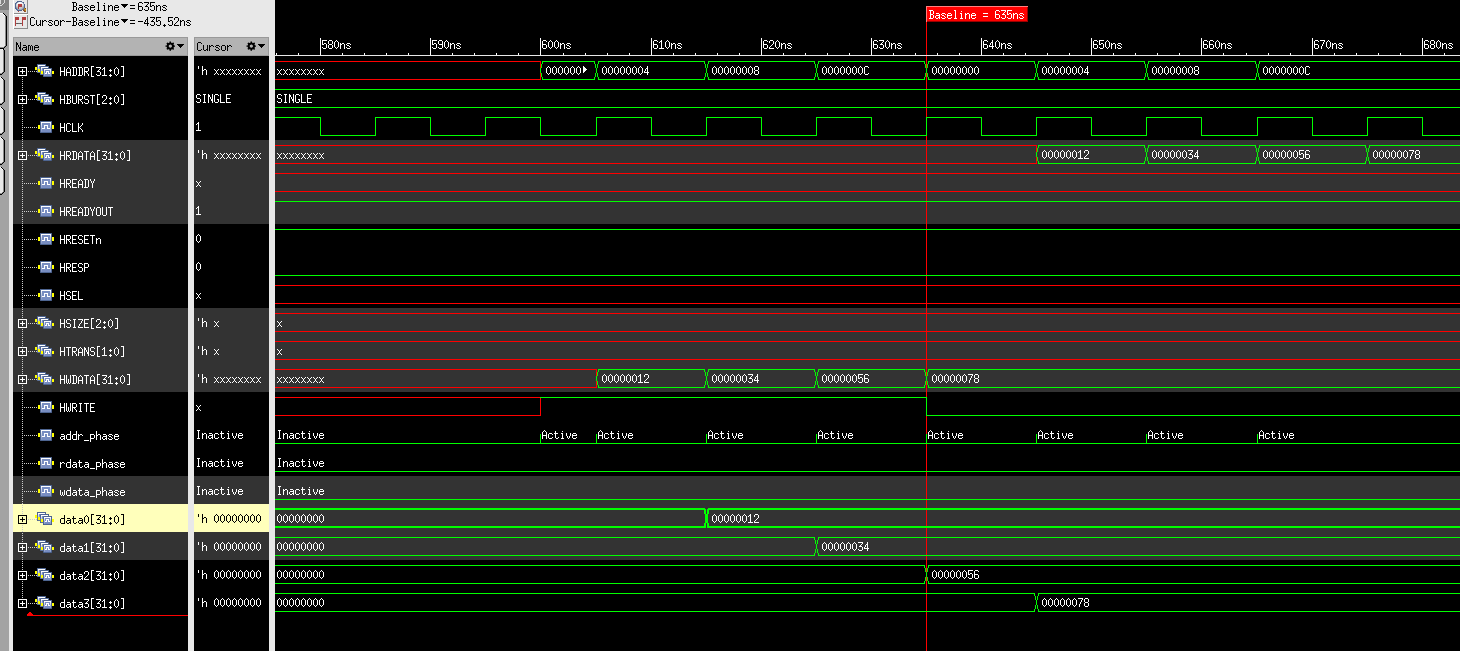

This is for read waveform without one cycle delay

My intention that read transaction should be executed without one cycle delay but can’t read.